# The Semantics Stack of the Verisoft XT Project

Christoph Baumann

KTH Royal Institute of Technology Stockholm, Sweden

### January 25, ENTROPY 2018

cbaumann@kth.se

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

January 25, ENTROPY 2018 1 / 30

< ロ > < 同 > < 回 > < 国

Introduction

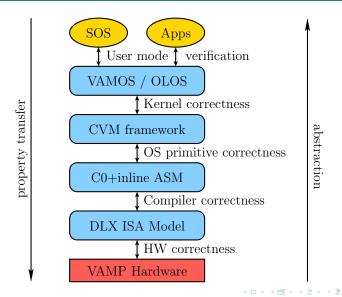

# Verisoft: Pervasive OS Verification (2003-2007)

C. Baumann (KTH Stockholm)

# • Pervasive Formal Verification of Realistic Computer Systems

< 67 >

- Pervasive Formal Verification of Realistic Computer Systems

- Hardware Verfication ((infineon))

- Automotive Software (

Audi,

BOSCH)

- E b

- Pervasive Formal Verification of Realistic Computer Systems

- Hardware Verfication ((infineon))

- Automotive Software (

Audi,

BOSCH)

- Avionics Project ( SYSGO, SEE , )

- Hypervisor Project (Microsoft\*)

- H - N

- Pervasive Formal Verification of Realistic Computer Systems

- Hardware Verfication ((infineon))

- Automotive Software (

Audi,

BOSCH)

- Hypervisor Project (Microsoft\*)

- tool development: VCC

- E b

Results:

- large portions of code verified

- kernel and hardware specifications

- powerful verifier VCC

< 同 > < 三 > < 三 >

Results:

- large portions of code verified

- kernel and hardware specifications

- o powerful verifier VCC

Main issue: missing semantical underlay

< A >

Results:

- large portions of code verified

- kernel and hardware specifications

- powerful verifier VCC

Main issue: missing semantical underlay

- weak memory model

- memory management units with TLBs

- mixed C & assembly code

- interruptible C

- multi-threaded C

- interleaved user and device steps

- concurrent compiler correctness

# DISCLAIMER

Lots of people involved in the presented work:

- Artem Alekhin

- Geng Chen

- Ernie Cohen

- Ulan Degenbaev

- Mikhail Kovalev

- Petro Lutsyk

- Jonas Oberhauser

- Hristo Pentchev

- Prof. Wolfgang J. Paul

- Norbert Schirmer

- Sabine Schmaltz

- Andrey Shadrin

#### Introduction

*"Theory of Multi Core Hypervisor Verification"* Cohen, Paul, and Schmaltz, 2013

æ

<ロ> <同> <同> < 回> < 回>

- system programmer's model

- memory management unit

- cache control instructions

- pipelining artifacts

- weak memory model

- undefined behaviour

3 A

- system programmer's model

- memory management unit

- cache control instructions

- pipelining artifacts

- weak memory model

- undefined behaviour

- software conditions

- system programmer's model

- memory management unit

- cache control instructions

- pipelining artifacts

- weak memory model

- undefined behaviour

- software conditions

Machine readable models:

- rudimentary PowerPC model

- x64:

*"Formal Specification of the x86 Instruction Set Architecture"* Ulan Degenbaev, PhD thesis, 2011

э

イロト イポト イヨト イヨト

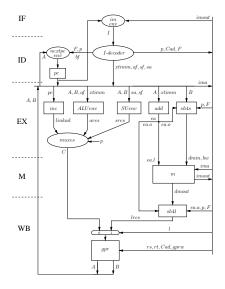

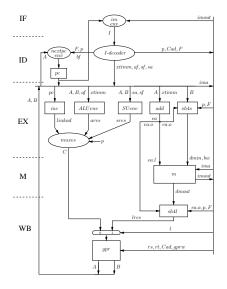

MIPS instruction core with x86 memory system:

Image: A mage: A ma

- MMUs / TLBs

- interrupts

- devices

- caches

- store buffers

- MIPS instruction core with x86 memory system:

- MMUs / TLBs

- interrupts

- devices

- caches

- store buffers

- correctness proof for pipelined multicore implementation with

- MIPS instruction core with x86 memory system:

- MMUs / TLBs

- interrupts

- devices

- caches

- store buffers

- correctness proof for pipelined multicore implementation with

- find software conditions of ISA

38 N

Recent text books / lecture notes:

- "A Pipelined Multi-core MIPS Machine".

M. Kovalev, S. M. Müller, and W. J. Paul, Springer, 2014

- "System Architecture: An Ordinary Engineering Discipline".

W. J. Paul, C. Baumann, P. Lutsyk, and S. Schmaltz, Springer, 2016

- "Multicore System Architecture".

W. J. Paul, P. Lutsyk, and J. Oberhauser, Springer, to be published

4 3 5 4 3

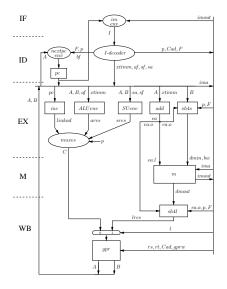

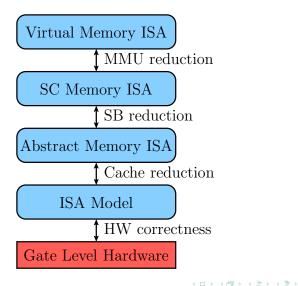

### Reducing caches, store buffers, and MMU

3

イロト イポト イヨト イヨト

#### Cache abstraction

- MOESI protocol

- give parallel implementation

- correctness proof and simulation

#### Theorem

If every address is accessed in the same cache mode by all processors then caches are invisible.

Proof: *"A Pipelined Multi-core MIPS Machine"* Kovalev, Müller, and Paul, 2014

Ξ.

<ロ> <同> <同> < 同> < 同> < 同> -

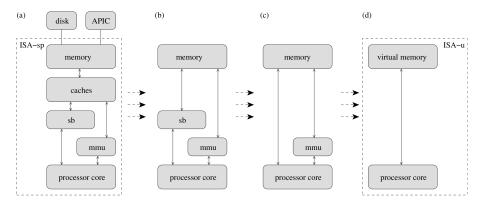

buffer writes locally before commiting them to memory

< A >

- buffer writes locally before commiting them to memory

- can ruin sequential consistency in multicore processors:

$$\{x = 0 \land y = 0\}$$

(x := 1; R1 = y) || (y := 1; R2 = x)

$$\{\neg(R1 = 0 \land R2 = 0)\}$$

- buffer writes locally before commiting them to memory

- can ruin sequential consistency in multicore processors:

$$\{x = 0 \land y = 0\}$$

(x := 1; R1 = y) || (y := 1; R2 = x)

$$\{\neg(R1 = 0 \land R2 = 0)\}$$

• need to add fences which flush the store buffer:

$$(x := 1; FENCE; R1 = y) || (y := 1; FENCE; R2 = x)$$

- buffer writes locally before commiting them to memory

- can ruin sequential consistency in multicore processors:

$$\{x = 0 \land y = 0\}$$

(x := 1; R1 = y) || (y := 1; R2 = x)

$$\{\neg (R1 = 0 \land R2 = 0)\}$$

• need to add fences which flush the store buffer:

$$(x := 1; FENCE; R1 = y) || (y := 1; FENCE; R2 = x)$$

• efficient flushing policy:

Mark concurrent accesses to the same address as shared!

- buffer writes locally before commiting them to memory

- can ruin sequential consistency in multicore processors:

$$\{x = 0 \land y = 0\}$$

(x := 1; R1 = y) || (y := 1; R2 = x)

$$\{\neg (R1 = 0 \land R2 = 0)\}$$

• need to add fences which flush the store buffer:

$$(x := 1; FENCE; R1 = y) || (y := 1; FENCE; R2 = x)$$

- efficient flushing policy:

- Mark concurrent accesses to the same address as shared!

- Between any shared write and shared read, flush the store buffer!

- buffer writes locally before commiting them to memory

- can ruin sequential consistency in multicore processors:

$$\{x = 0 \land y = 0\}$$

(x := 1; R1 = y) || (y := 1; R2 = x)

$$\{\neg (R1 = 0 \land R2 = 0)\}$$

• need to add fences which flush the store buffer:

(x := 1; FENCE; R1 = y) || (y := 1; FENCE; R2 = x)

• efficient flushing policy:

Mark concurrent accesses to the same address as shared!

Between any shared write and shared read, flush the store buffer!

- concurrent accesses: exists an interleaved execution schedule:

- · consecutive steps by different threads access the same address

- at least one of them is modifying its value

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

12/30

### Theorem

If the system without store buffers fulfills the flushing policy then it is a sound abstraction of the system with store buffers

Proofs:

- *"A Better Reduction Theorem for Store Buffers"*. Cohen and Schirmer, tech report 2009 / ITP 2010

- "Store Buffer Reduction with MMUs: Complete Paper-and-pencil Proof". Chen, Cohen, and Kovalev, tech report 2013 / VSTTE 2014

- *"Store Buffer Reduction Theorem and Application"*. Geng Chen, PhD thesis, 2016

- *"A Simpler Reduction Theorem for x86-TSO"*. Jonas Oberhauser, VSTTE 2015

- "Justifying The Strong Memory Semantics of Concurrent High-Level Programming Languages for System Programming". Jonas Oberhauser, PhD thesis, 2018

C. Baumann (KTH Stockholm)

### Eliminating the MMU

#### Proof:

*"TLB Virtualization in the Context of Hypervisor Verification"* Mikhail Kovalev, PhD thesis, 2013

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

Hardware Abstraction

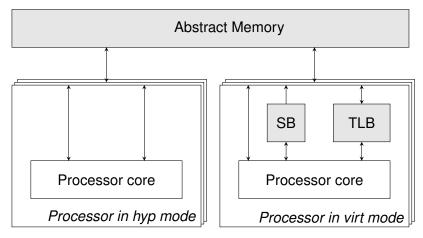

# **Hardware Abstraction**

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

January 25, ENTROPY 2018 15 / 30

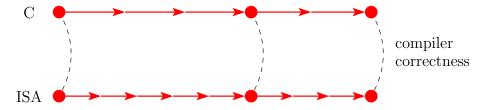

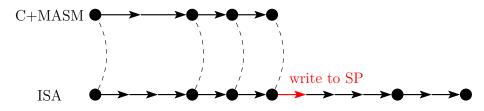

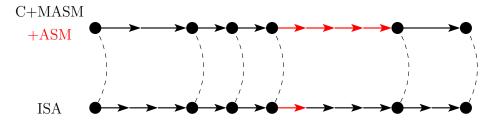

### Sequential Compiler Correctness (Verisoft style)

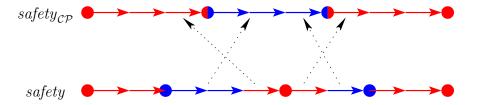

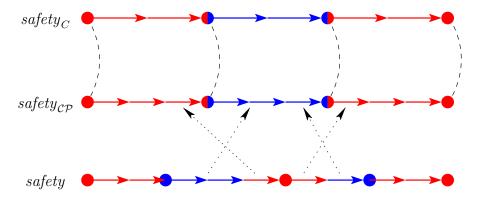

$\bullet$  = consistency point (CP)

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

January 25, ENTROPY 2018 16 / 30

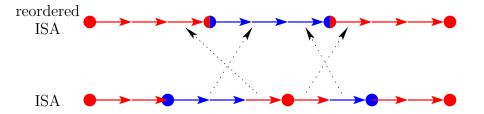

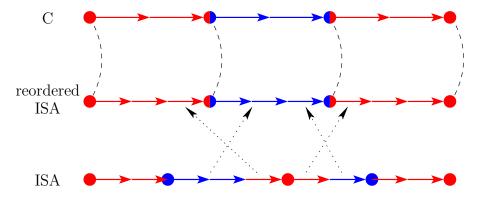

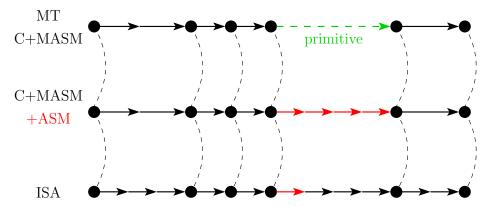

Concurrent compiler correctness

(D) < ((()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) <

Concurrent compiler correctness

∃ >

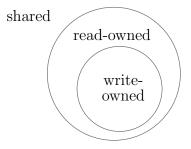

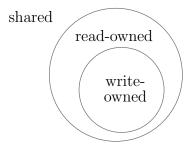

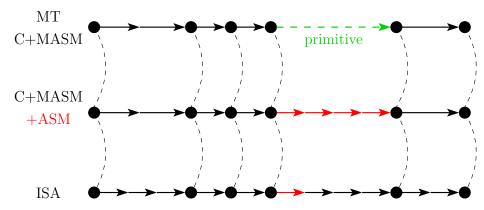

### Concurrent compiler correctness

# Ownership model:

2

Ownership model:

Ownership memory access policy:

- Iocal steps: only read read-owned, only write write-owned

- shared steps: read if not write-owned by other thread, write if not owned by other thread

- ownership transfer via annotations at shared steps

- write-ownership = exclusive ownership = local addresses

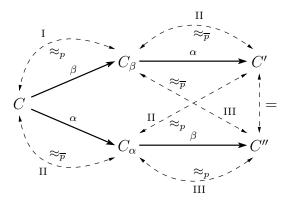

## **Commutativity of Local Steps**

For two steps  $\alpha$ ,  $\beta$  by different processors were  $\alpha$  is local we have:

$$safe(C, \beta \alpha) \land C \stackrel{\beta \alpha}{\longmapsto} C' \iff safe(C, \alpha \beta) \land C \stackrel{\alpha \beta}{\longmapsto} C'$$

< 67 >

# **Commutativity of Local Steps**

For two steps  $\alpha$ ,  $\beta$  by different processors were  $\alpha$  is local we have:

$$safe(C, \beta \alpha) \land C \stackrel{\beta \alpha}{\longmapsto} C' \iff safe(C, \alpha \beta) \land C \stackrel{\alpha \beta}{\longmapsto} C'$$

All computations starting in C are ownership-safe and fulfill safety property P.

< ロ > < 同 > < 回 > < 回 > < 回 > <

All computations starting in C are ownership-safe and fulfill safety property P.

safety<sub>CP</sub>(C, P):

• All CP block computations starting in C are ownership-safe and fulfill safety property P.

< 67 >

• All computations starting in *C* are ownership-safe and fulfill safety property *P*.

safety<sub>CP</sub>(C, P):

- All *CP* block computations starting in *C* are ownership-safe and fulfill safety property *P*.

- $at\_most\_one\_shared_{CP}(C)$ :

- On all CP block computations starting in C there is at least one CP between two shared steps of the same processor

• All computations starting in *C* are ownership-safe and fulfill safety property *P*.

safety<sub>CP</sub>(C, P):

- All *CP* block computations starting in *C* are ownership-safe and fulfill safety property *P*.

- $at\_most\_one\_shared_{CP}(C)$ :

- On all CP block computations starting in C there is at least one CP between two shared steps of the same processor

# **Order Reduction Theorem**

$safety_{\mathcal{CP}}(\mathcal{C}, \mathcal{P}) \land at\_most\_one\_shared_{\mathcal{CP}}(\mathcal{C}) \implies safety(\mathcal{C}, \mathcal{P})$

Proof: "Ownership-Based Order Reduction and Simulation in Shared-Memory Concurrent Computer Systems" Christoph Baumann, PhD thesis, 2014

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

Safety Transfer

э

< 17 ▶

Safety Transfer

Must preserve ownership-safety and atomicity of shared accesses!

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

January 25, ENTROPY 2018 21 / 30

C Intermediate Language (C-IL)

- C with low-level control flow (gotos & function calls)

- pointer arithmetics

- function pointers

- compiler intrinsics

- operational semantics

- compiler consistency relation for MIPS86

Formalization:

*"Towards the Pervasive Formal Verification of Multi-Core Operating Systems and Hypervisors Implemented in C"* Sabine Schmaltz, PhD thesis, 2013

Ξ.

ヘロン 人間 とくほ とくほ と

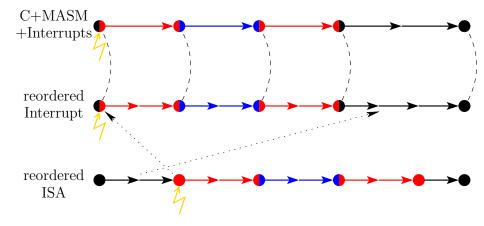

- OS kernels written in C + Assembler

- C functions call assembly procedures

- Assembly procedures call C functions

< A >

- OS kernels written in C + Assembler

- C functions call assembly procedures

- Assembly procedures call C functions

- MASM: stack and control flow abstractions

- OS kernels written in C + Assembler

- C functions call assembly procedures

- Assembly procedures call C functions

- MASM: stack and control flow abstractions

- Mixed semantics: C-IL+MASM

Formalization:

"Integrated Semantics of Intermediate-Language C and Macro-Assembler for Pervasive Formal Verification of Operating Systems and Hypervisors from VerisoftXT" Schmaltz and Shadrin, VSTTE 2012

"Mixed Low- and High Level Programming Language Semantics and Automated Verification of a Small Hypervisor" Andrey Shadrin, 2012

#### C + Interrupts

э

(D) < ((()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) <

#### C + Interrupts

< 17 ▶

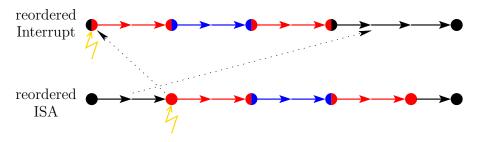

C + Interrupts

Necessary conditions:

- transparency: handlers restore the interrupted thread correctly and do not modify its local data.

- *independency*: handlers do not use the register content of the interrupted thread.

Necessary conditions:

- transparency: handlers restore the interrupted thread correctly and do not modify its local data.

- independency: handlers do not use the register content of the interrupted thread.

Formalization:

- *"Sound semantics of a high-level language with interprocessor interrupts"*. Hristo Pentchev, PhD thesis, 2016

- *"Order Reduction for Multi-core Interruptible Operating Systems"*. Jonas Oberhauser, VSTTE, 2016

・ 同 ト ・ ヨ ト ・ ヨ ト

э

< 17 ▶

*"Provably sound semantics stack for multi-core system programming with kernel threads".* Artem Alekhin, PhD thesis, 2017

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

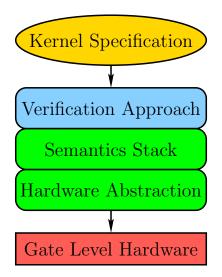

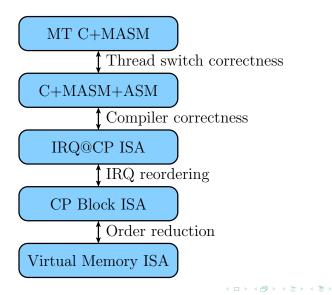

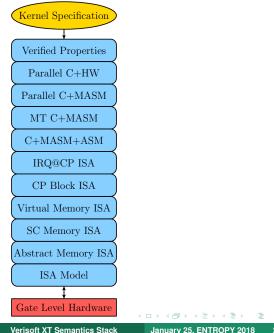

# **Semantics Stack**

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

January 25, ENTROPY 2018 27 / 30

Summing up:

- theory for pervasive multicore OS verification

- hardware abstraction

- semantics stack

- many general theorems ۲

< A >

Summing up:

- theory for pervasive multicore OS verification

- hardware abstraction

- semantics stack

- many general theorems

Open issues:

- MIPS86: out-of-order execution + MMU + SB

- semantic stack without reduced MMU?

- thread migration

- machine-checked theories & proofs

- soundness proof for verification with VCC

Summary

# Thank You!

# **Questions?**

C. Baumann (KTH Stockholm)

Verisoft XT Semantics Stack

January 25, ENTROPY 2018 30 / 30

・ 同 ト ・ ヨ ト ・ ヨ